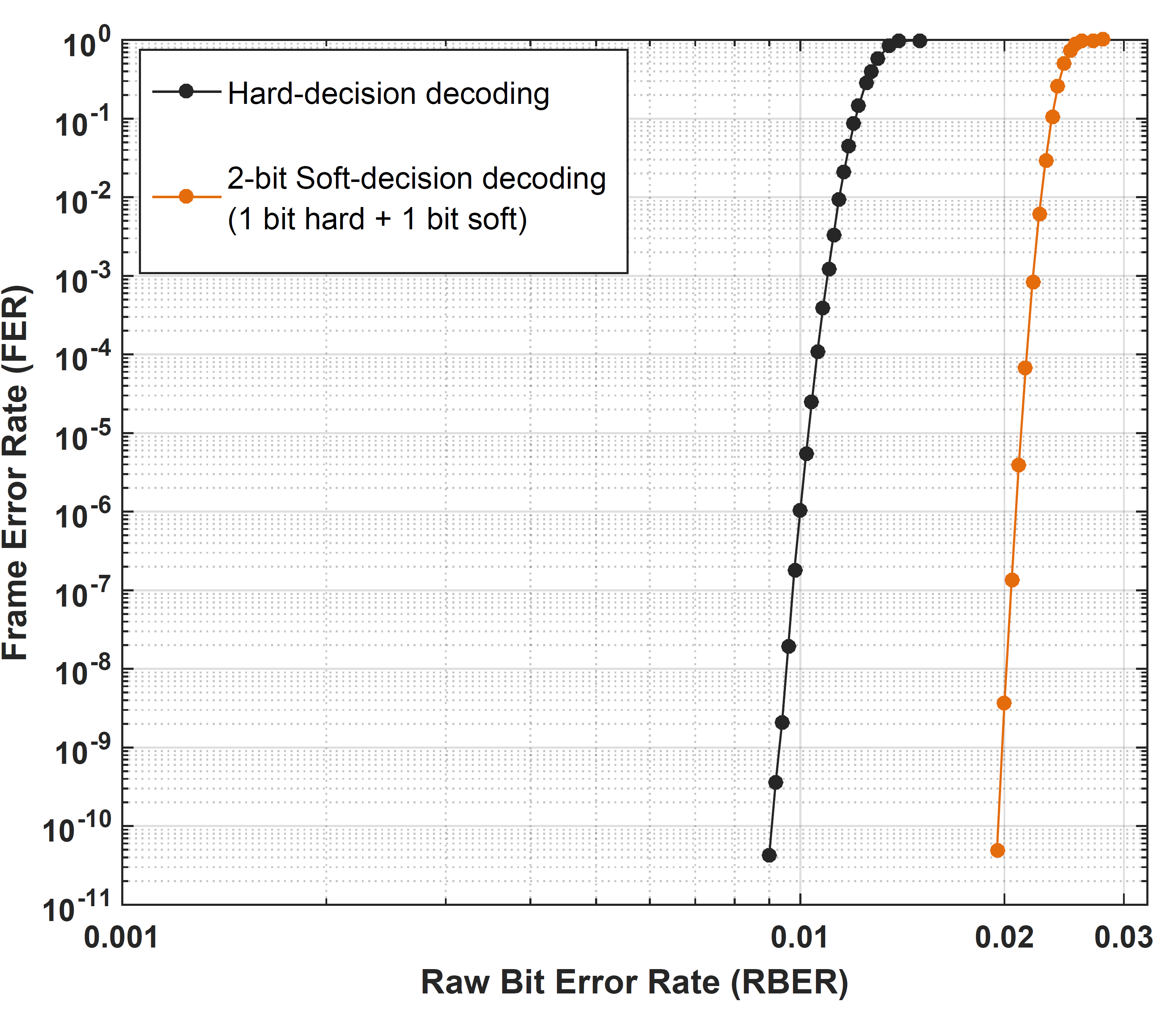

Error-correction Performance for 3D QLC NAND

FER vs RBER plot generated from FPGA simulation

Technology

Enabling reliable low-cost high-capacity flash storage for data centers and hyperscale storage.

Whether you are looking to use an FPGA or an ASIC flash controller to transition to the latest 3D NAND flash memories, our fully scalable and customizable solutions will enable your transition while providing the highest endurance and performance for your storage.

Best-in-class error-correction performance achieved by FAIDTM core technology

Traditional LDPC solutions require large resource usage and power that scales prohibitively with the ever-increasing throughput requirements, and the issue of error floor prevents them from achieving the required low error-rates without adding complexity.

Using a unique patented technology (finite alphabet iterative decoding) that was invented based on years’ of research by the founding team, our FAIDTM core solutions provide the strongest error-correction capability with highly scalable throughputs and no occurrence of error floor.

Our FAIDTM Value Proposition

We provide custom designed proprietary FAIDTM LDPC IP cores with technical consulting, development and support services that achieve